Due to a problem with the Intel® FPGA Power and Thermal Calculator (PTC) in the Intel® Quartus® Prime Pro Edition Software version 20.3 and earlier, you may see this error even if there are still available pins when differential input pins are used and the VCCIO voltages of all I/O banks are not 2.5V in Intel® Stratix® 10 devices.

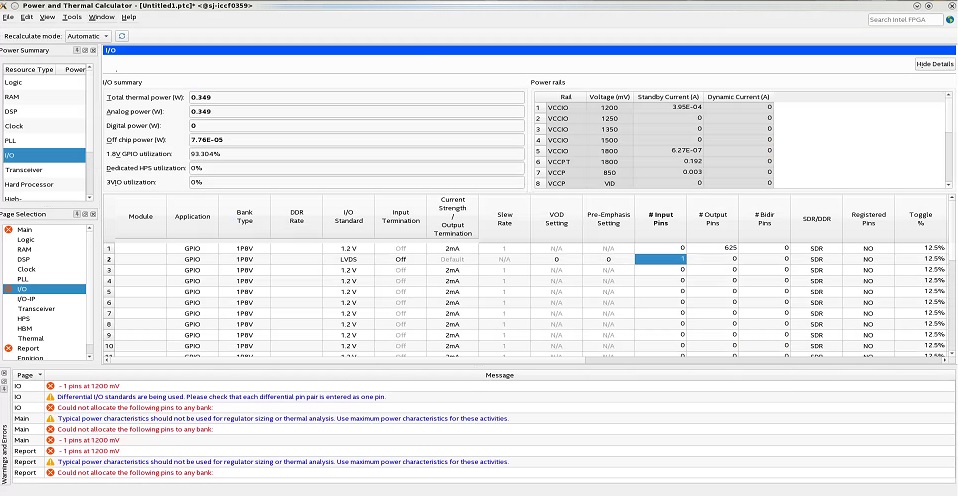

Here is an example.

Device: 1SG280H

Package: F50

Number of user I/O: 672

Number of I/O bank: 14

Number of pin pre I/O bank: 48

User I/O usage:

1.2 V output * 625 pins

LVDS input * 1 pair

In this case, since 625 pins are used for 1.2 V output, the VCCIO voltages of 14 I/O banks are 1.2 V.

LVDS input is powered by VCCPT, not VCCIO. So a pair of LVDS input should be able to be assigned to remaining pins, but the PTC incorrectly displays an error as shown in the following image.

You can safely ignore this error.

This problem is fixed starting with the Intel® FPGA Power and Thermal Calculator (PTC) in the Intel® Quartus® Prime Pro Edition Software version 21.3.