Visible to Intel only — GUID: lcp1493520992679

Ixiasoft

Visible to Intel only — GUID: lcp1493520992679

Ixiasoft

16.10.3. Understanding the Custom Traffic Generator User Interface

The interface has three tabs:

- Data tab

- Address tab

- Loops tab

Data Tab

The Data tab is divided into Data Pins and Data Mask Pins sections.

The Data Pins section helps with customizing the patterns selected for the data pins. You can choose between two options for Data Mode:

- PRBS The default write data to all the data pins.

- Fixed Pattern Lets you specify a pattern to be written to the memory.

Select the All Pins option when you want to write the same data pattern to all the data pins. If data must be individually assigned to the data pins, you must enter the data value for each individual pin. The width of the data entered is based on the AVL_TO_DQ_WIDTH_RATIO, which is based on the ratio of the memory clock to the user clock.

All data bytes are enabled by default; the Data Mask Pins section lets you disable any of the bytes if you want to. To disable data bytes individually, select Test data mask.

You can choose between two options for Data Mode:

- PRBS Specifies the PRBS pattern to enable or disable data bytes. A 1 denotes a data byte enabled, while a 0 denotes a data byte being masked or disabled.

- Fixed Pattern Lets you enable or disable individual bytes. You can apply byte enables to all pins or to individual bytes. A 1 denotes a data byte enabled, while a 0 denotes a data byte being masked or disabled.

Address Tab

The Address tab lets you configure sequential, random, or random sequential (where the initial start address is random, but sequential thereafter) addressing schemes. The Address tab is divided into Address Mode and Address Configuration sections.

The Address Mode section lets you specify the pattern of addresses generated to access the memory. You can choose between three address modes :

- Sequential Each address is incremented by the Sequential address increment value that you specify. You also specify the Start Address from which the increments begin.

- Random Each address is generated randomly. (You set the number of random addresses on the Loops tab.)

- Random Sequential Each address is generated randomly, and then incremented sequentially. You specify the number of sequential increments in the Number of sequential addresses field.

The Address Configuration section contains the settings with which you configure the address mode that you chose in the Address Mode section. The following settings are available:

- Start address Specifies the starting address for Sequential Address Mode. The maximum address value that can be reached is 1FF_FFFF. (The Traffic Generator 2.0 will accept higher values, but wraps back to 0 after the maximum value has been reached.) The Start address setting applies only to Sequential Address Mode.

- Number of sequential addresses Specifies the number of sequential addresses generated after the first random address generated. This setting applies only in Random sequential mode.

- Sequential address increment Specifies the size of increment between each address in the Sequential address mode and Random sequential address mode.

- Return to start address Specifies that the address value generated return back to the value entered in the Start Address field, after a block of transactions to the memory has completed. This setting applies only to Sequential address mode.

- Address masking Masking provides additional options for exploring certain specific address spaces in memory:

- Disabled does not enable masking, and increments address based on the selected Address Mode.

- Fixed cycling allows you to restrict the addressing to a specific row or a specific bank, which you can specify in the corresponding Mask Value field.

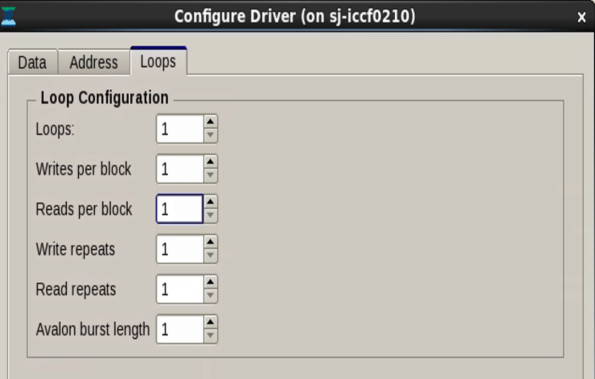

Loops Tab

The Loops tab lets you order the transactions to the memory as desired. A unit size of transactions to the memory is defined as a block; a block includes a set of write transaction(s) immediately followed by a set of read transaction(s).

The Loops tab provides the following configuration options:

- Loops Specifies the number of blocks of transactions to be sent to the memory. This option helps to extend the range of addresses that the controller can access. The address range is incremented as each loop is executed, unless you specify Return to Start Address, which causes each loop to begin from the same start address. The range of supported values for the Loops option is from 1 to 4095.

- Writes per block Specifies the size of the block (that is, the number of consecutive write operations that can be issued in a single block). The range of values for this option is as follows:

- When address masking is disabled, the number of writes per block supported is 1 to 4094.

- When address masking is enabled, the maximum number of writes issued inside a block is 255.

- Reads per block Specifies the number of consecutive read operations that can be issued in a single block, immediately following the consecutive writes issued. The number of reads per block should be identical to the number of writes per block, because data mismatches can occur when the two values are not identical. The range of values for this option is as follows:

- When address masking is disabled, the number of reads per block supported is 1 to 4094.

- When address masking is enabled, the maximum number of reads issued inside a block is 255.

- Write repeats Specifies the number of times each write command is issued in repetition to the same address. A maximum number of 255 repeat write transactions can be issued. The repeat writes are issued immediately after the first write command has been issued.

- Read repeats Specifies the number of times each read command is issued in repetition to the same address. A maximum number of 255 repeat read transactions can be issued. The repeat reads are issued immediately after the first read command has been issued.

- Avalon burst length Specifies the length of each Avalon burst. The value of this field should be less than the Sequential address increment specified on the Address tab. The number of write and read repeats default to 1 if the Avalon burst length is greater than 1.