Visible to Intel only — GUID: snz1474418824955

Ixiasoft

1.1. Reference Design Overview

1.2. Floorplanning

1.3. Getting Started

1.4. Reference Design Components

1.5. Compiling the Reference Design

1.6. Bringing Up the Reference Design

1.7. Testing the Reference Design

1.8. Extending the Reference Design with Custom Persona

1.9. Reference Design Files

1.10. Document Revision History for AN 813: Hierarchical Partial Reconfiguration over PCI Express* Reference Design for Intel® Arria® 10 Devices

Visible to Intel only — GUID: snz1474418824955

Ixiasoft

1.1. Reference Design Overview

The reference design consists of the following components:

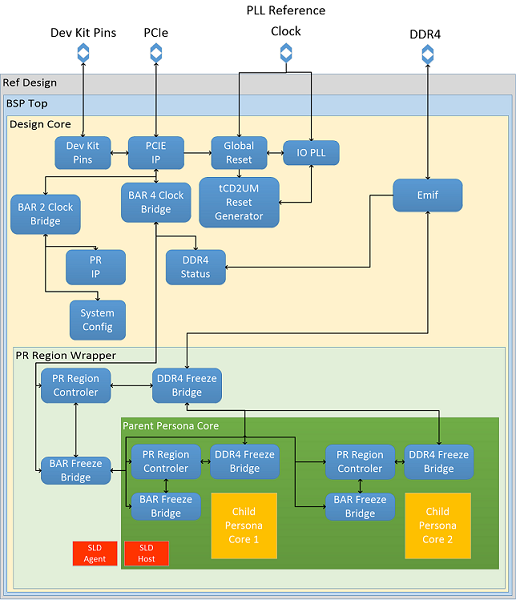

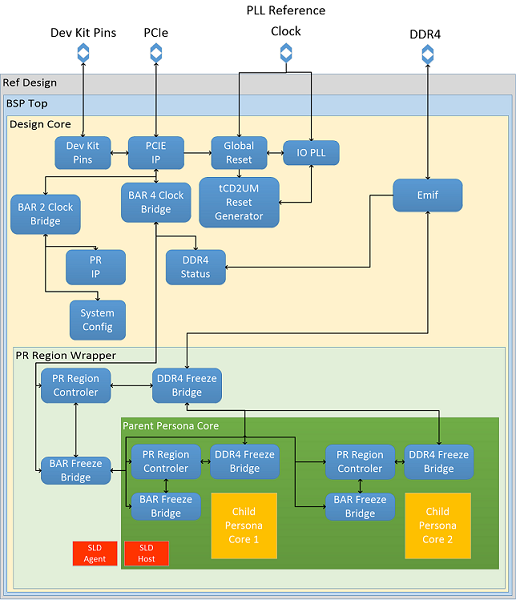

Figure 1. Intel® Arria® 10 PCIe* Reference Design Block Diagram

- a10_pcie_reference_design—top-level reference design wrapper connecting the board support package (BSP) subsystem to the device pins.

- bsp_top—design top-level containing all subsystems. Includes the Intel® Arria® 10/Cyclone 10 Hard IP for PCI Express* , the External Memory Interfaces Intel® FPGA IP, and the design top module. This abstraction layer allows simulation of the design top module through simulated Avalon® memory-mapped transactions.

- design_core—design core that generates of the PR region and the interface components, such as clock crossing Avalon memory mapped logic and pipeline logic, clocks, and the global reset.

Related Information