Visible to Intel only — GUID: mwh1409958798326

Ixiasoft

Visible to Intel only — GUID: mwh1409958798326

Ixiasoft

5.9. Specify Parameters in the Platform Designer Component Editor

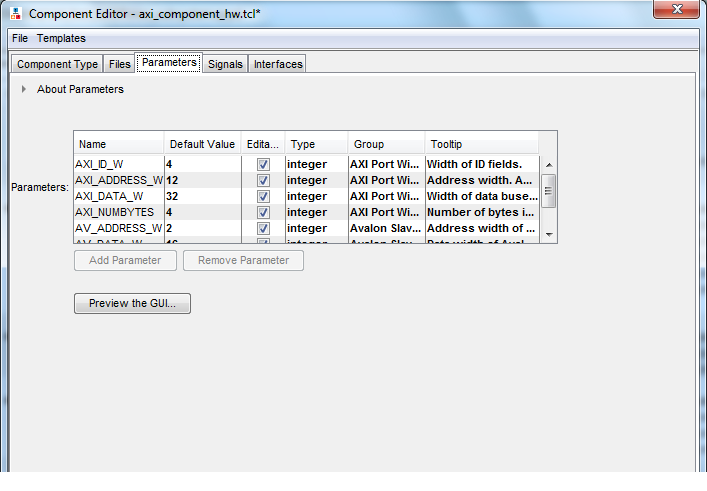

The Parameters tab allows you specify the parameters that are used to configure instances of the component in a Platform Designer system. You can specify various properties for each parameter that describe how to display and use the parameter. You can also specify a range of allowed values that are checked during the validation phase. The Parameters table displays the HDL parameters that are declared in the top-level HDL module. If you have not yet created the top-level HDL file, the top-level synthesis file template created from the Files tab include the parameters that you create on the Parameters tab.

When the component includes HDL files, the parameters match those defined in the top-level module, and you cannot add or remove them on the Parameters tab. To add or remove the parameters, edit your HDL source, and then re-analyze the file.

If you create a top-level template HDL file for synthesis with the Component Editor, you can remove the newly-created file from the Synthesis Files list on the Files tab, make your parameter changes, and then re-analyze the top-level synthesis file.

You can use the Parameters table to specify the following information about each parameter:

- Name—Specifies the name of the parameter.

- Default Value—Sets the default value for new instances of the component.

- Editable—Specifies whether or not the user can edit the parameter value.

- Type—Defines the parameter type as string, integer, boolean, std_logic, logic vector, natural, or positive.

- Group—Allows you to group parameters in parameter editor.

- Tooltip—Allows you to add a description of the parameter that appears when the user of the component points to the parameter in the editor.

On the Parameters tab, you can click Preview the GUI at any time to see how the declared parameters appear in the parameter editor. Parameters with their default values appear with checks in the Editable column. Editable parameters cannot contain computed expressions. You can group parameters under a common heading or section in the editor with the Group column, and a tooltip helps users of the component understand the function of the parameter. Various parameter properties allow you to customize the component’s parameter editor, such as using radio buttons for parameter selections, or displaying an image.

_hw.tcl Created from Entries in the Parameters Tab

In this example, the first add_parameter command includes commonly-specified properties. The set_parameter_property command specifies each property individually. The Tooltip column on the Parameters tab maps to the DESCRIPTION property, and there is an additional unused UNITS property created in the code. The HDL_PARAMETER property specifies that the value of the parameter is specified in the HDL instance wrapper when creating instances of the component. The Group column in the Parameters tab maps to the display items section with the add_display_item commands.

# # parameters # add_parameter AXI_ID_W INTEGER 4 "Width of ID fields" set_parameter_property AXI_ID_W DEFAULT_VALUE 4 set_parameter_property AXI_ID_W DISPLAY_NAME AXI_ID_W set_parameter_property AXI_ID_W TYPE INTEGER set_parameter_property AXI_ID_W UNITS None set_parameter_property AXI_ID_W DESCRIPTION "Width of ID fields" set_parameter_property AXI_ID_W HDL_PARAMETER true add_parameter AXI_ADDRESS_W INTEGER 12 set_parameter_property AXI_ADDRESS_W DEFAULT_VALUE 12 add_parameter AXI_DATA_W INTEGER 32 ... # # display items # add_display_item "AXI Port Widths" AXI_ID_W PARAMETER ""

If an AXI slave's ID bit width is smaller than required for your system, the AXI slave response may not reach all AXI masters. The formula of an AXI slave ID bit width is calculated as follows:

maximum_master_id_width_in_the_interconnect + log2 (number_of_masters_in_the_same_interconnect)

For example, if an AXI slave connects to three AXI masters and the maximum AXI master ID length of the three masters is 5 bits, then the AXI slave ID is 7 bits, and is calculated as follows:

5 bits + 2 bits (log2(3 masters)) = 7

| AXI Master Parameters | AXI Slave Parameters |

|---|---|

| readIssuingCapability | readAcceptanceCapability |

| writeIssuingCapability | writeAcceptanceCapability |

| combinedIssuingCapability | combinedAcceptanceCapability |

| readDataReorderingDepth |