Visible to Intel only — GUID: mcu1525397372049

Ixiasoft

Test Case

The simulation test case performs the following steps:

- Configures the MAC, TX and RX FIFO buffers, and Ethernet packet generator.

- Ethernet packet generator generates and transmits 32 packets with 66 bytes and random payload to the Avalon® -ST TX path.

- Waits until all the packets are loopback and received on Avalon® -ST RX path.

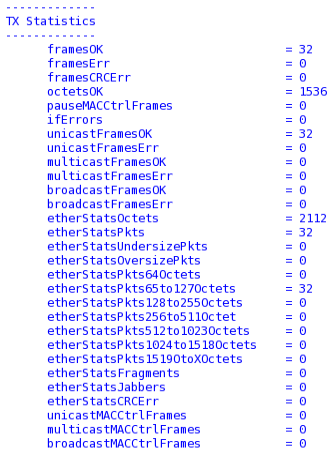

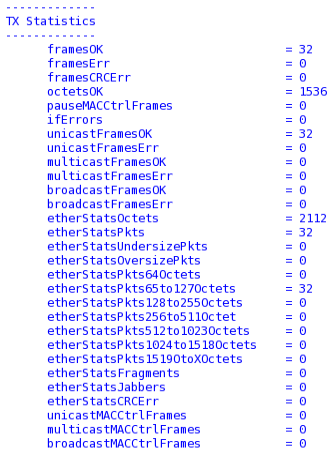

- At the end of the simulation, the transcript window displays the number of good and bad packets, which monitored by Ethernet packet monitor (refer to Figure 4), and the values of the MAC statistic counters (refer to Figure 5 and Figure 6). The transcript window also displays "Simulation PASSED" if all statistics error counters are zero and the RX MAC statistics counters are equal to the TX MAC statistics counters.

Note: The simulation of this design requires approximately 404800 ns to complete.

- In the simulation waveform window (refer to Figure 7), the measurement cursors indicates the roundtrip latency for serial loopback to show that time taken to transmit the first data from Avalon® -ST TX datapath to the Avalon® -ST RX datapath.

Figure 4. Status of Ethernet Packet Monitor

Figure 5. TX Statistics Counter

Figure 6. RX Statistics Counter

Figure 7. Simulation Waveform