Visible to Intel only — GUID: iga1447716961193

Ixiasoft

Visible to Intel only — GUID: iga1447716961193

Ixiasoft

3.3.4. PCI Interface

Intel offers a wide range of PCI local bus solutions that you can use to connect a host processor to an FPGA. You can implement the PCI Intel® FPGA IP function using the Parameter Editor or Platform Designer design flow.

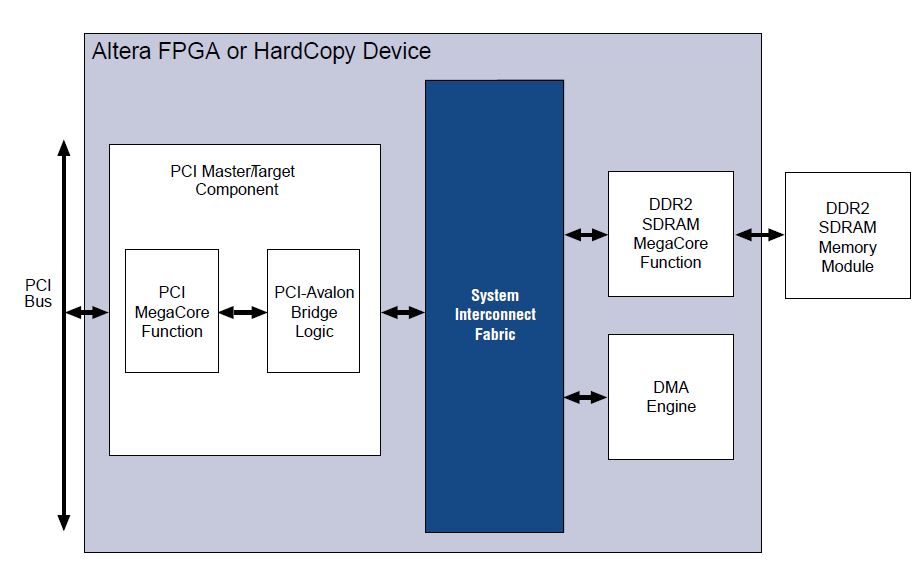

The PCI Platform Designer flow is an easy way to implement a complete Avalon-MM system which includes peripherals to expand system functionality without having to be well-acquainted with the Avalon-MM protocol. The figure below illustrates a Platform Designer system using the PCI Intel® FPGA IP function. You can parameterize the PCI Intel® FPGA IP function with a 32- or 64-bit interface.

For more information refer to the PCI Compiler User Guide.