Visible to Intel only — GUID: uzt1482113562368

Ixiasoft

Visible to Intel only — GUID: uzt1482113562368

Ixiasoft

Test Result Comments

In each test case, both the JESD204B transmitter and JESD204B receiver IP core successfully initialize from CGS phase, ILAS phase, and until user data phase.

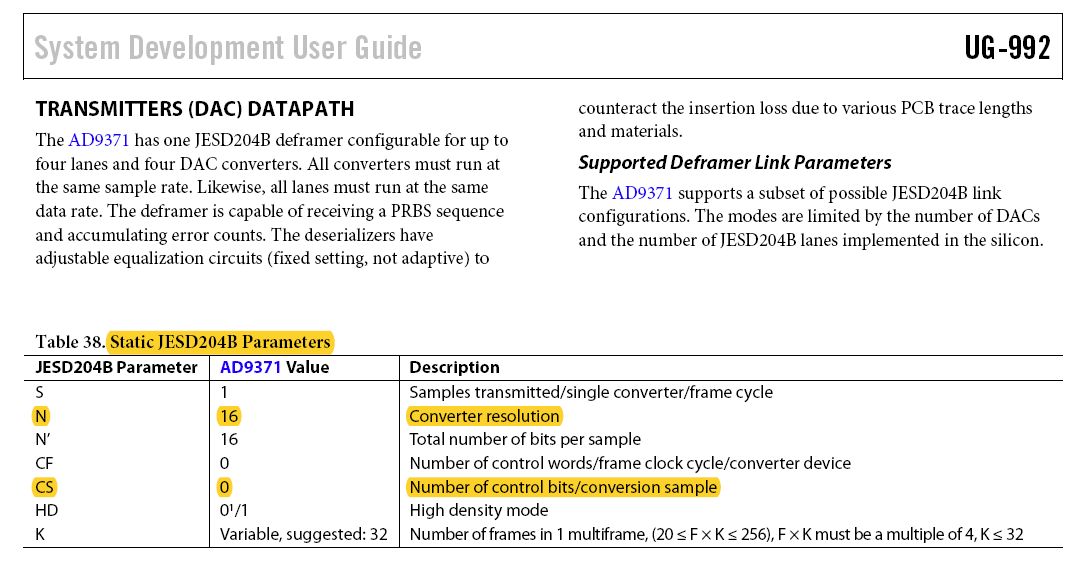

The test results for JESD204B transmitter are marked with Pass with comments because the deframer of AD9371 raises IRQ due to ILAS configuration mismatch. The conflicting ILAS parameters are N value and CS value. The AD9371 deframer register contains the following JESD204B parameter values N=14 and CS=2 while FPGA transmits ILAS with following JESD204B parameter N=16 and CS=0. The FPGA is configured with JESD204B parameters as per values defined in AD9371-User-Guide-UG-992 document available at the time of testing (refer Figure 15). Otherwise the behavior of the JESD204B transmitter IP core meets the passing criteria.

The monotone sine wave from FPGA is transmitted into RF domain successfully at desired frequency and when loopbacked into ADC, the original monotone sine wave is received back.

In the deterministic latency measurement, consistent total latency is observed across the JESD204B transmitter link and JESD204B receiver link.